AMD a déjà reçu les premiers chipsets fonctionnels de 2 nm Zen 6, avec quelques mois avant le lancement commercial

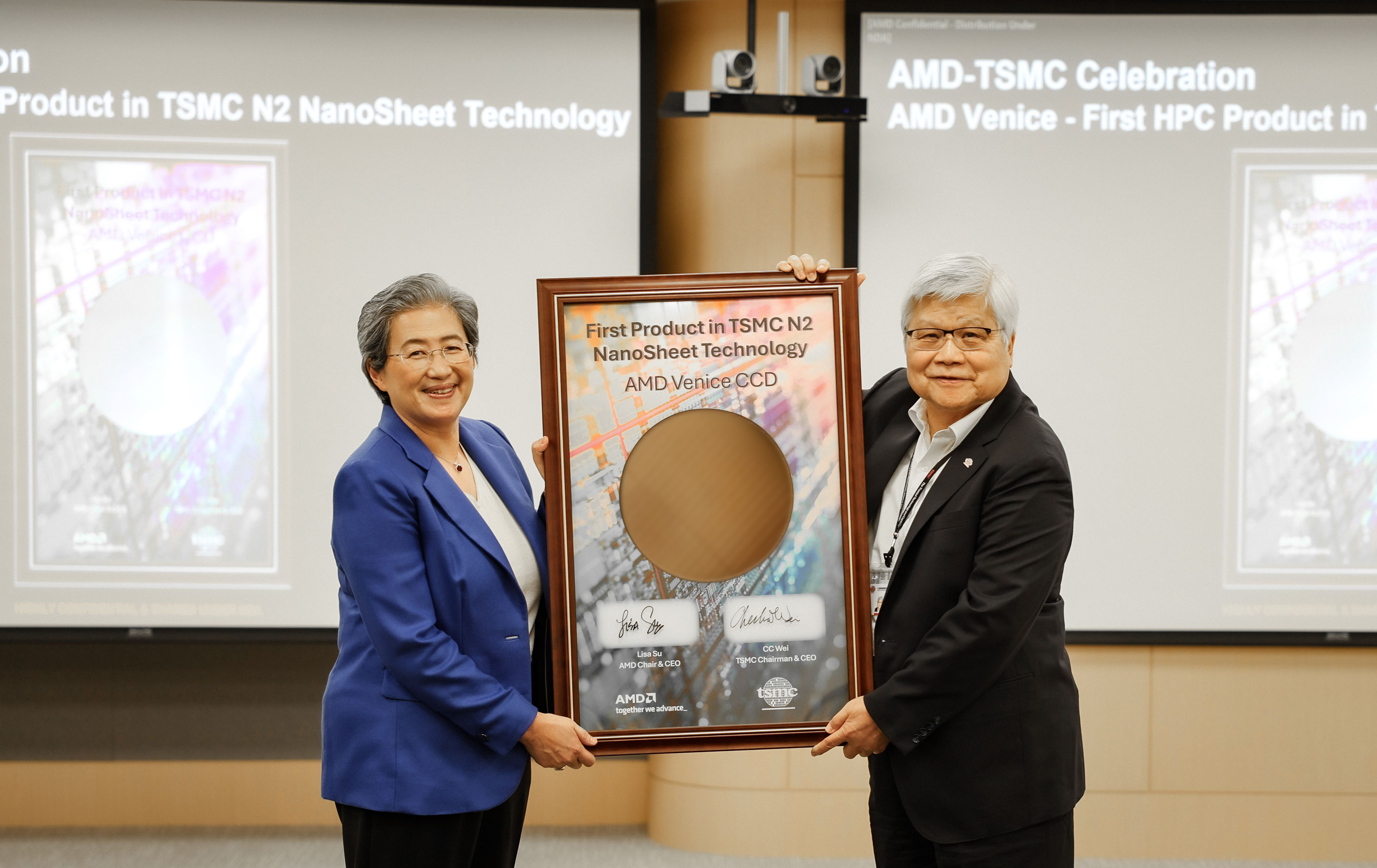

Tandis qu'Intel continue de lutter et de retarder la sortie de nouveaux Xeons, AMD a annoncé de manière inattendue qu'il a déjà reçu les premiers cristaux fonctionnels fabriqués sur un process de 2 nm. Nous parlons du CCD (core) pour la prochaine génération de processeurs EPYC Venice basés sur l'architecture Zen 6.

Voici ce que nous savons

AMD a confirmé que les chipsets ont réussi les tests initiaux et l'alimentation, c'est-à-dire qu'ils sont "en marche". Ils sont fabriqués à la fab TSMC utilisant le nouveau process N2, qui utilise des transistors Gate-All-Around (GAA), la prochaine étape après FinFET.

Selon TSMC, le nouveau process peut soit réduire la consommation d'énergie de 24-35 % soit augmenter les performances de 15 % avec la même consommation d'énergie. Il permet également d'augmenter le nombre de transistors pouvant être placés sur la même surface (15 % de densité en plus par rapport à la génération de 3 nm).

Les processeurs Venice seront disponibles en 2026 et seront partie intégrante de la 6ème génération d'EPYC. De plus, AMD a confirmé qu'il a déjà testé des chipsets EPYC de 5ème génération fabriqués dans la nouvelle fab Fab 21 de TSMC en Arizona, ce qui signifie que la société diversifie sérieusement sa capacité de production, ce qui est une bonne nouvelle au milieu des turbulences de la chaîne d'approvisionnement mondiale.

Le PDG d'AMD, Lisa Su, a qualifié cette sortie d'exemple de coopération approfondie avec TSMC et de prochaine étape dans le développement de l'informatique haute performance.

Zen 6 est l'architecture future des processeurs d’AMD qui poursuivra le développement de la ligne Zen. Il est prévu d'apporter une réduction supplémentaire de la latence, une amélioration des performances mémoire et un meilleur scalabilité des cœurs. Selon des rapports non officiels, Zen 6 utilisera une nouvelle topologie de cache et une microarchitecture FP-block mise à jour.

TSMC N2 est un processus avancé de 2 nm qui utilise des transistors GAA (Gate-All-Around) pour la première fois. Cela permet de réduire la fuite de courant, d'augmenter les fréquences et de diminuer la consommation d'énergie.

Source: ir.amd.com